随着FPGA和CPLD技术的飞速发展,软核处理器在嵌入式系统设计中的地位日益重要。其中,NIOS II作为Altera(现Intel FPGA)推出的经典软核处理器,以其灵活性和可定制性,在FPGA、CPLD乃至ASIC设计中广受青睐。本文结合电子技术论坛中的热门讨论,特别是“小炮与锆石9”软核学习案例,深入探讨NIOS II硬件框架结构,帮助开发者更好地掌握这一关键技术。

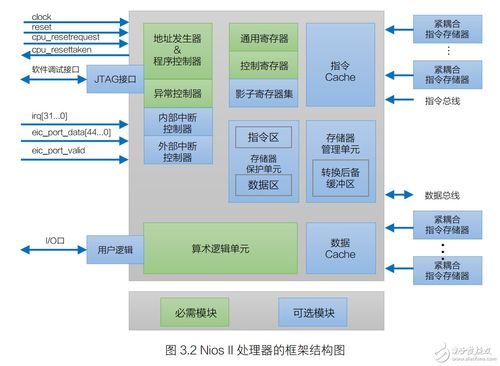

NIOS II处理器是一个基于RISC架构的软核,它允许用户根据具体应用需求定制指令集、外设和内存接口。其硬件框架主要包括以下核心组件:处理器核心、总线系统(如Avalon总线)、中断控制器、定时器、以及用户自定义外设。在“小炮与锆石9”学习项目中,学习者通过实际搭建NIOS II系统,验证了其模块化设计的优势,例如通过Avalon总线轻松集成UART、SPI等外设,实现高效的片上系统(SoC)设计。

NIOS II的深入学习离不开对FPGA和CPLD平台的熟悉。在电子技术论坛上,许多开发者分享了使用Intel Quartus等工具进行NIOS II软核配置的经验。例如,在锆石9开发板上,用户可以通过QSYS工具快速构建硬件系统,定义处理器参数和总线连接,然后使用Nios II Software Build Tools (SBT) 编写和调试软件代码。这种软硬件协同设计方法,不仅提升了开发效率,还降低了ASIC原型设计的门槛。

NIOS II框架的灵活性使其适用于多种应用场景,从简单的控制任务到复杂的数据处理。论坛中,有用户通过“小炮”项目实现了实时信号处理系统,展示了NIOS II在性能优化和资源管理方面的能力。与ASIC设计结合时,NIOS II可以作为验证核心,帮助测试定制逻辑的功能,这在专业电子论坛上被广泛讨论为“软硬结合”的最佳实践。

NIOS II硬件框架结构的学习是FPGA/CPLD开发者的重要课题。通过论坛交流和实际项目如“小炮与锆石9”,开发者可以深入理解其架构细节,提升电子技术开发水平。随着人工智能和物联网的兴起,NIOS II等软核技术将继续在专业电子领域发挥关键作用,推动创新应用的实现。