在计算机系统结构的学习中,流水线技术是提升处理器性能的核心设计思想之一。它通过将指令执行过程分解为多个阶段,并让多条指令在不同阶段重叠执行,从而实现了指令级并行,显著提高了处理器的吞吐率。本部分复习笔记将系统梳理流水线技术的关键概念,并探讨其与底层电子技术开发的紧密互动与共同演进。

一、流水线技术的基本原理与性能分析

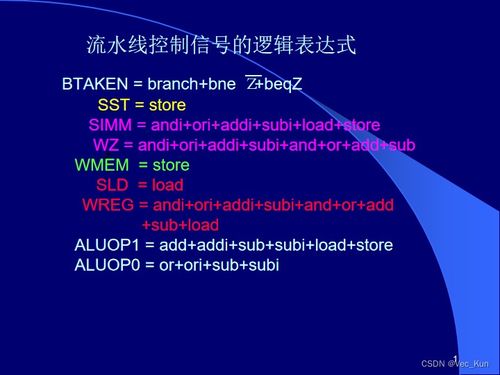

经典的5级RISC流水线(取指IF、译码ID、执行EX、访存MEM、写回WB)是理解流水线的基础模型。其理想加速比公式为 Speedup = Tnon-pipeline / Tpipeline ≈ N(阶段数),但实际中由于结构冒险、数据冒险和控制冒险的存在,加速比会低于理想值。

- 冒险与解决策略:

- 结构冒险:硬件资源冲突。解决方法包括资源重复(如分离指令和数据缓存)和流水线停顿。

- 数据冒险:后续指令需要等待前序指令的数据。解决方法包括转发(旁路)技术、流水线停顿以及编译器调度(静态调度)。

- 控制冒险:分支指令导致的指令流改变。解决方法包括分支预测(静态预测、动态预测如两位饱和计数器、分支目标缓冲BTB)、延迟槽技术等。

- 性能度量:吞吐率(单位时间完成的指令数)和加速比是核心指标。流水线深度增加可以提高时钟频率,但也会增加冒险开销和寄存器开销,存在一个最优深度点。

二、现代流水线技术的深化:超标量与动态调度

为了进一步挖掘指令级并行,现代处理器超越了基本的线性流水线:

- 超标量技术:每个时钟周期发射多条指令到多条并行工作的流水线中。这需要更复杂的取指、译码和提交逻辑,以及多端口寄存器和缓存。

- 动态调度(乱序执行):以Tomasulo算法及其变种为代表,通过保留站、重排序缓冲(ROB)等硬件结构,允许指令在操作数就绪后立即执行,克服了假数据依赖(名相关),极大地提高了硬件利用率。动态调度与分支预测、推测执行紧密结合,是现代高性能CPU(如Intel Core、AMD Ryzen系列)的核心。

三、流水线技术与电子技术开发的共生演进

流水线设计的每一次飞跃,都深深植根于同时代电子技术的发展,并反过来推动其进步。

- 晶体管微缩与时钟频率提升:在半导体工艺遵循摩尔定律飞速发展的年代,晶体管尺寸缩小使得单芯片上可以集成更复杂的流水线控制逻辑(如更强大的分支预测器、更大的ROB)。更高的晶体管开关速度直接支撑了更深流水线和更高主频的设计,追求更高的指令吞吐率。

- 功耗墙与能效优先设计:当工艺进入纳米尺度后,漏电功耗急剧增加,时钟频率和电压提升遇到瓶颈(功耗墙)。这迫使流水线设计从单纯追求高频深流水线(如Intel NetBurst架构的Pentium 4)转向更注重能效的设计:

- 适度流水线深度:避免过深的流水线带来的分支误预测惩罚和功耗开销。

- 多核与片上众核:在单线程ILP挖掘接近极限后,通过并行处理技术(线程级并行TLP、数据级并行DLP)来提升整体性能,流水线技术成为每个核心的基础。

- 异构计算与特定流水线:为图形处理(GPU)、AI计算(NPU)等特定任务设计高度定制化的流水线(如SIMD、SIMT流水线),实现极高的能效比。

- 存储墙与内存层次结构优化:处理器速度远快于主存,访存延迟成为瓶颈。流水线设计必须与缓存层次结构协同:

- 更智能的预取器被集成在流水线的访存阶段,预测并提前加载数据。

- 非阻塞缓存设计允许流水线在缓存缺失时继续执行其他不相关指令,掩盖延迟。

- 这些都需要在芯片上集成更大、更智能的SRAM缓存,这是电子技术实现的直接体现。

- 先进封装与系统级集成:随着2.5D/3D封装、Chiplet等电子集成技术的发展,可以将不同工艺、不同功能的计算单元(如CPU核、GPU核、IO单元)集成在一起。这使得系统级的“流水线”或“处理链路”成为可能,例如将数据从网络接口通过高速互连直接“流水”到处理单元,再“流水”到存储单元,整个路径的优化超越了单芯片内流水线的范畴。

四、与展望

流水线技术是计算机体系结构中连接软件指令流与硬件物理实现的桥梁。从经典的线性流水线到复杂的超标量乱序执行引擎,其演进始终与半导体工艺、电路设计、功耗管理和封装技术等电子技术开发同频共振。面对后摩尔时代,流水线技术将继续与新型器件(如存算一体)、光互连、近内存计算等电子技术创新结合,在提升性能、降低能耗、支持新兴应用(如AI、量子计算经典控制)等方面探索新的形态,持续推动计算系统向前发展。

(本笔记旨在提纲挈领,具体细节如算法实例、定量分析、具体型号处理器案例等需结合教材与课堂内容进行深化复习。)